# BBB000 COMPUTER REFERENCE MANUAL

홍철왕왜 문양명(BR달왕왕임정말홍권) 승규는 영영광

# **BBOO COMPUTER REFERENCE MANUAL**

© WANG LABORATORIES, INC., 1970 Tewksbury, Mass. 01876 Telephone (617) 851-7311 TWX 710 343-6769

# TABLE OF CONTENTS

| ١.         | INTRODUCTION                                                          | 1  |

|------------|-----------------------------------------------------------------------|----|

| H.         | GENERAL SPECIFICATIONS                                                | 2  |

| 111.       | CPU REGISTER ORGANIZATION                                             | 3  |

|            | A. Addressable Registers                                              | 4  |

|            | B. Non-Addressable Registers                                          | 5  |

| IV.        | MEMORY ORGANIZATION AND ADDRESSING                                    | 7  |

|            | A. Current Page Addressing                                            | 7  |

|            | B. Absolute Page Addressing                                           | 8  |

|            | C. Indirect Addressing                                                | 8  |

|            | D. Auto-Index Indirect Address Reference                              | 8  |

|            | E. Immediate Reference                                                | 9  |

| <b>V</b> . | INSTRUCTION FORMATS                                                   | 10 |

|            | A. Format 1 – Memory Reference Instruction (Without Auto-Index)       | 10 |

|            | B. Format 2 – Memory Reference Instructions (With Auto-Index)         | 10 |

|            | C. Format 3 – Immediate Reference Instructions                        | 10 |

|            | D. Format 4 – Register Setting and Skip Instructions                  | 10 |

|            | E. Format 5 – Shift/Rotate Instructions (A-Register)                  | 11 |

|            | F. Format 6 – Mini Instructions (Current Page Jump)                   | 11 |

| VI.        | WANG 3300 INSTRUCTION REPERTOIRE                                      | 12 |

|            | A. Memory Reference Group (Without Auto-Index)                        | 12 |

|            | B. Memory Reference Group (With Auto-Index)                           | 13 |

|            | C. Immediate Reference Group                                          | 15 |

|            | D. Shift and Rotate Group                                             | 16 |

|            | E. Conditional Jump Group                                             | 17 |

|            | F. Conditional Skip Group (A-Register, Status Register, I/O Register) | 18 |

|            | G. Register Transfer and Manipulation Group (With Micro Jumps)        | 19 |

|            | H. Input/Output and Interrupt Group                                   | 20 |

| VII.       | Input/Output and Interrupt Organization                               | 22 |

|            | A. Modes of Input/Output Operation                                    | 22 |

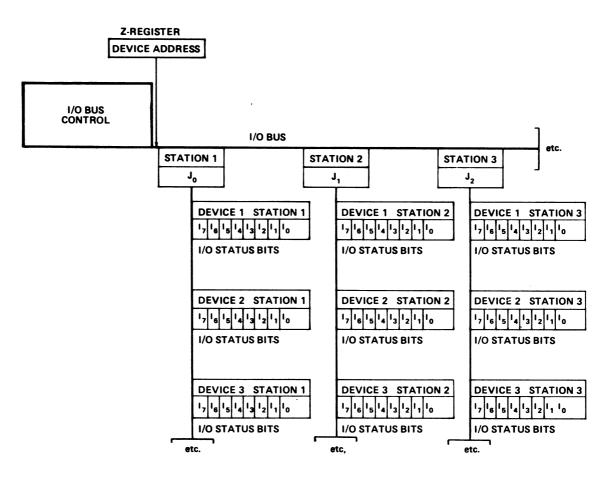

|            | B. I/O Bus Structure Organization                                     | 22 |

|            | C. I/O Status Registers                                               | 23 |

|            | D. Interrupt Operations and Instructions                              | 25 |

|            | E. I/O Instructions                                                   | 26 |

# TABLE OF CONTENTS (Concl'd)

| VIII. | 331  | 5 TELETYPE TERMINAL OPERATION                       | 27 |

|-------|------|-----------------------------------------------------|----|

|       | Α.   | Operational Characteristics                         | 27 |

|       | В.   | I/O Status Register Settings                        | 27 |

|       | С.   | Read and Write Programming Procedures               | 29 |

|       | D.   | Program Examples                                    | 30 |

|       | Ε.   | Teletype Device Buffer Addresses                    | 33 |

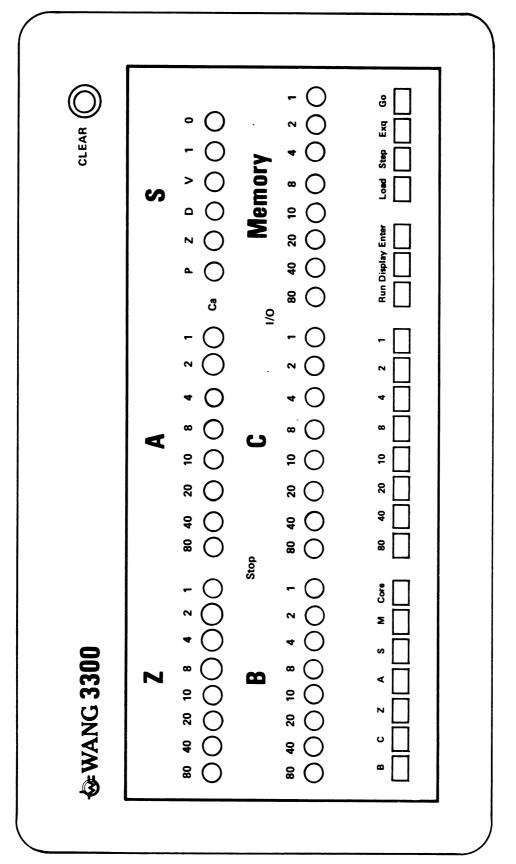

| IX.   | CON  | TROL CONSOLE OPERATING PROCEDURES                   | 34 |

|       | Α.   | Turn-On Procedures                                  | 34 |

|       | В.   | Display Contents of Single Memory Location          | 34 |

|       | С.   | Read Consecutive Memory Locations                   | 34 |

|       | D.   | Modify the Contents of a Single Memory Location     | 34 |

|       | Ε.   | Modify the Contents of Consecutive Memory Locations | 34 |

|       | F.   | Enter or Modify Data in Registers                   | 34 |

|       | G.   | Single Step Program Execution                       | 35 |

|       | Н.   | Automatic Program Execution                         | 35 |

|       | I.   | Execute Command from Control Panel                  | 35 |

| APPEN | DIXE | S .                                                 |    |

|       | •    |                                                     |    |

| А. |                                    | 39 |

|----|------------------------------------|----|

| В. | Alphabetic List of Instructions    | 43 |

| С. | Table of Instructions by OP Code   | 47 |

| D. | Wang 3300 ASCII Character Code Set | 49 |

Ç

# LIST OF ILLUSTRATIONS

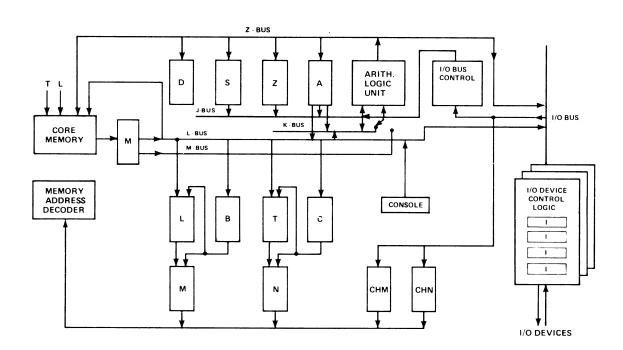

| Figure | 1 | Block Diagram of the Wang 3300 CPU Organization | 3  |

|--------|---|-------------------------------------------------|----|

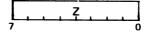

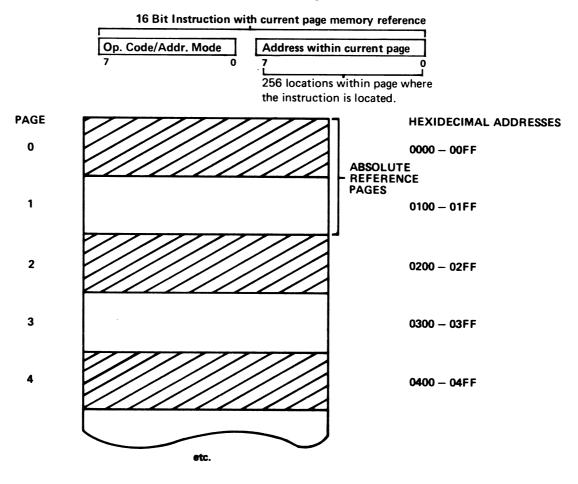

|        | 2 | Wang 3300 Memory Page Format                    | 7  |

|        | 3 | Typical I/O Bus Station Organization            | 24 |

|        | 4 | Wang 3300 Console                               | 37 |

|        |   |                                                 |    |

# LIST OF TABLES

| Table | 1 | Teletype I/O Status Register Settings During Data Transfer | 28 |

|-------|---|------------------------------------------------------------|----|

|       | 2 | 3300 Computer Console Switches and Indicators              | 36 |

#### I. INTRODUCTION

The Wang 3300 is an integrated circuit general purpose mini computer. Unlike most computers in this class, it was specifically designed to be the central processor for multi-terminal time-sharing applications for higher level language systems. The Wang 3300 design incorporates such features as:

- A powerful repertoire of 68 instructions, including 21 memory reference instructions.

- A flexible and powerful I/O logic design which includes an I/O bus structure to handle up to 128 low and medium speed peripheral devices and Direct Memory Access Channel logic to control high speed devices at transfer rates up to 300,000 cps.

- A highly efficient priority interrupt structure which handles up to 128 priority interrupt levels and incorporates device address interrupt acknowledgement to reduce interrupt processing time.

Memory expandability up to 65k bytes to accommodate large system applications.

- Nine modes of addressing, including a unique auto-increment/auto-decrement indirect addressing mode throughout all of memory. In this mode the indirect address is decremented before and incremented after single or double byte memory transfers. This produces a true push-pop access mode for handling table and list processing efficiently. In many applications, it provides the flexibility and speed equivalent to an unlimited number of index registers, and also eliminates the time consuming bookkeeping requirements associated with index registers.

- Six arithmetic instructions which operate in both binary and decimal mode. In decimal mode, 4 bit decimal groups are operated on in decimal arithmetic. This feature eliminates the inaccuracies and time inefficiencies associated with decimal to binary conversion and binary arithmetic, and provides a multi-precision capability.

The Wang 3300 is a byte-oriented computer, but it also has a number of double byte operand memory reference commands. This in essence provides the best features of both 8 bit and 16 bit computers. In many areas where the processing involves higher level languages, a single byte or character is commonly referenced. A 16 bit fetch is inefficient and often involves additional masking logic. However, in those instances in which 16 bit transfers are required, Wang 3300 double byte commands accommodate them.

The Wang 3300 is designed specifically to meet the high performance requirements of time-sharing systems. However, a modular design and a flexible and powerful I/O structure and instruction repertoire enable the 3300 to meet a great variety of scientific and commercial applications in the both real-time and batch processing modes.

#### **II. GENERAL SPECIFICATIONS**

- Computer transfer logic 8 bit parallel binary

- Memory Cycle time 1.6 μ sec.

- Word Length 8 bits

- Instruction Length 16 bits

- Addressing Memory is segmented in 256 byte pages.

- The following addressing modes are available.

- Direct Absolute page (Page 0 or 1)

- Direct Current page

- Indirect Absolute page (Page 0 or 1)

- Indirect Current page

- Indirect, Absolute Page, Auto-Increment (Page 0 or 1)

- Indirect, Absolute Page, Auto-Decrement (Page 0 or 1)

- Indirect, Current Page, Auto-Increment

- Indirect, Current Page, Auto-Decrement

- Immediate

- Memory Type Magnetic core

- Memory Size From 4,096 to 65,536 bytes in increments of 4,096 bytes

- Arithmetic Modes- Binary Mode and Addressing 2's complement

- Decimal Mode 4 bit BCD Complement Instructions - 1's complement or 9's complement

- Speed

- Add: 8 bit binary 4.8  $\mu$ sec Add: 8 bit decimal - 4.8  $\mu$ sec

- Add: 16 bit binary 6.4  $\mu$ sec

- Add: 16 bit decimal 6.4  $\mu$  sec

- Multiply: floating point, (8 digit decimal mantissa) 4 ms

- Input Output

I/O Bus structure which controls up to 128 devices

- Multiplex Mode (character Buffers)

- Direct Memory Access channel Mode

- Interrupt Device Station Groups

- 128 Priority Levels

- Peripheral Equipment

- Wang 3310 I/O Writer (Modified IBM Selectric)

- Keyboard Input

- Typed Output at 15 cps

- Wang 3315 33-ASR Teletype, Model TBE

- Keyboard Input

- Typed Output at 10 cps

- Paper Tape Reader 10 cps

- Punch Tape Punch 10 cps

- Off-line paper tape preparation, reproduction, listing

- Remote phone line terminal capability

- Wang 1103A Acoustic Coupler (with Automatic Answer-Back)

- To interface the 3300 for remote phone line connection

- Wang 1104A Acoustic Coupler

- To interface the 3315 teletypes for remote phone line connection

- Wang 3320 Magnetic Tape Cassette Drive Pair

- Tape Read 800 cps

- Tape Write 800 cps

- Rewind Speed 1 minute

- Tape Capacity 300,000 byte (max)

#### III. CPU REGISTER ORGANIZATION

Figure 1, a block diagram of the 3300 CPU organization, illustrates the data storage registers, memory and input/output control logic. The basic storage unit of memory is a byte (8 bits). All registers are 8 bits in length.

The A, Z, S, B, C, and I registers can be addressed or reset by computer instructions. The A and Z registers are general accumulator registers. The S register contains operational status and control bits. The B and C registers are the program instruction counter. The I register contains I/O status information.

The remaining control logic and registers are used in the execution of computer instructions, memory access and input/output. They are not addressable.

All arithmetic operations are performed in the Arithmetic Logic Unit. Arithmetic operations are performed in both binary and decimal mode. Binary arithmetic is performed in 2's complement where one byte assumes a value of from 0 to 255. In decimal mode, a byte containing two 4-bit decimal digits is operated on in decimal arithmetic. In decimal mode, a byte can assume values from 00 to 99.

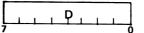

Information is fetched from memory in a one-byte path via the M register and the L-Bus and M-Bus to various registers. Information is transferred to memory in a one byte path via the Z bus. The memory address is contained in the M and N registers from where it is fetched and decoded.

Information is transferred between input/output device control logic and either the A register or directly to and from memory via the I/O Bus, L-Bus, Z-Bus, and Arithmetic Logic Unit.

The following section contains a detailed description of the CPU registers.

#### FIG. 1. BLOCK DIAGRAM OF THE WANG 3300 CPU ORGANIZATION

#### A. Addressable Registers

The following registers can be addressed or modified by computer instructions:

(1) A-Register

The A-register is an 8 bit general purpose register used primarily as the arithmetic accumulator, and for logical operations, bit manipulation and testing.

#### (2) Z-Register

The Z register is an 8 bit general purpose register. It is independently addressable, but is not generally used in arithmetic, logical, and testing operations like the A-register. It is however treated as a high order extention of the A-register for double byte commands (Double load, Double unload, Double add to Memory, Double shifts, etc.).

| (3) <b>S-Register</b><br>(Status Register) | NOT<br>USED | Ρ | с | z | D | v | s <sub>1</sub> s <sub>0</sub> | ] |

|--------------------------------------------|-------------|---|---|---|---|---|-------------------------------|---|

|                                            | 7           | 6 | 5 | 4 | 3 | 2 | 1 0                           |   |

The Status Register is made up of 7 bits which act and are set independently of one another, but may be addressed as a group with certain status register instructions. Two status bits, P and D, control absolute addressing and arithmetic modes. Others, such as C, Z, and V, are set after the execution of certain instructions to indicate the final results of the instruction operation.

The status register bits are:

The setting of the P bit controls what memory page is referenced by memory reference commands which are set up in an absolute page addressing format. If P is set to 0, page zero is referenced (locations 0 to 255). If P is set to 1, Page 1 is referenced, (locations 256 to 511). P is set and reset by status register instructions only, (ONS, OFS, TSAJ, TASJ).

$$\begin{array}{c} C \\ \hline C \\ \hline S \\ \hline \end{array} \qquad - Carry Bit (S_{S}) \\ \hline C = 1 Carry \\ C = 0 No Carry \\ \hline \end{array}$$

The C status bit (carry bit), is set after the execution of a number of arithmetic and comparison commands. The value of the carry from the high order bit or digit of the last arithmetic operation sets C, (TO 0 or 1). The previous setting of C is added into the lower order bit or digit for arithmetic instructions with carry.

| Z | - Last Value Zero (S <sub>4</sub> ) | Z = 1 Result Zero     |

|---|-------------------------------------|-----------------------|

| 4 |                                     | Z = 0 Result Non-zero |

The Z status bit is set after the execution of most load, register transfer, arithmetic, compare and logical instructions. Z is set to 1 if the final result of the arithmetic, logical or load operation was a zero, (result of both bytes for double commands). If it is set to 0, the result was not zero.

| D | - Decimal Arithmetic Mode Indicator (S <sub>3</sub> ) D = 0 Binary Mode |

|---|-------------------------------------------------------------------------|

| 3 | D = 1 Decimal Mode                                                      |

The setting of the D status bit controls the arithmetic mode for arithmetic instructions. If D is set to 0 binary arithmetic is performed, if it is set to 1 decimal arithmetic is performed. Addressing arithmetic and compare instruction arithmetic will always be done in binary mode, regardless of D. D is set and reset by status register instructions only (ONS, OFS, TSAJ, TASJ).

V = 0 Result valid decimal no. V = 1 Result not valid decimal no.

The V status bit is set after the execution of many load, register transfers, arithmetic and compare instructions. The V status bit is set only when the computer is in decimal arithmetic mode (the D status bit = 1). V is set to 0 if the final result of the instruction was a valid decimal number (each 4 bit groups are 0 to 9), and it is set to 1 if it was not.

$$\begin{bmatrix} \mathbf{S}_1 \\ \mathbf{S}_0 \end{bmatrix} = \mathbf{S}_0 - \mathbf{U}$$

ser Status Bits ( $\mathbf{S}_1, \mathbf{S}_0$ )

The  $S_0$  and  $S_1$  bits of the status register are general purpose bits which can be set at the programmer's discretion for program control functions. They are set by status register instructions and typically tested with status register skip instructions.

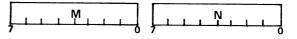

#### (4) **Program Counter Registers (B, C)**

| Β |   |     |  |

|---|---|-----|--|

| 7 | 0 | 7 0 |  |

These two registers contain the 16-bit address of the next instruction to be executed. The B register (most significant 8 bits) contains the page address, and the C register (least significant 8 bits) contains the address within page (0 to 255). A full address of from 0 to  $65,535_{10}$  can be expressed. The program counter is set by jump and skip commands.

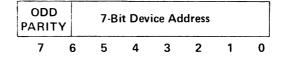

(5) I/O Register

The I/O control logic for each peripheral device contains the equivalent of this 8 bit register. The I/O Register bits indicate various conditions for that device, (ready, error, power off, etc.). The I/O register bits are always sensed with the address of the device stored in the Z-register. These bits are normally reset by I/O clear or enable operations.

#### B. Non-Addressable Registers

The following registers control and contain information for the execution of program instructions and memory access operations, but are not addressable by computer instructions.

(1) Instruction Register (D)

The 8 bit instruction register holds the instruction code byte of the instruction about to be executed.

(2) Operand Address Registers (M, N)

The M and N registers hold the full 16 bit address of the next byte to be fetched from or stored into memory. When instructions are fetched, M and N are set to the current value of the program counter. When a memory reference instruction is executed, M and N receive the final effective operand address.

(3) L-Register

This 8-bit register acts as an intermediate data transfer unit for memory reference, and register transfer operations.

#### (4) T-Register

This 8-bit temporary register is used as an intermediate data transfer unit for memory reference and register transfer operations.

# (5) M-Register

|   |   | M, | , |          |

|---|---|----|---|----------|

| 7 | - |    |   | <u> </u> |

ž

The M-Register functions as a memory data buffer, for Memory fetches. All data fetched from memory is temporarily stored in the M-register.

# (6) Arithmetic Logic Unit

This unit performs all arithmetic and logical operations and acts of a data transfer unit for register, memory reference and I/O operations.

#### (7) I/O Bus Control Unit

This unit controls the input/output transfer of data passing on the I/O Bus between the CPU and Device Control logic. It contains the G-register (General I/O) information.

#### (8) CHM, CHN

These registers contain the memory address for channel I/O operations.

#### (9) Input/Out Device Control Logic

The units control the operation for one or more I/O devices. The typical control unit also contains device data buffers and the I/O registers (I registers) for each controlled device.

# IV. MEMORY ORGANIZATION AND ADDRESSING

The basic unit of addressable memory is a byte, (8 bits). Memory is logically divided into 256 bytes groups called pages. Figure 2 illustrates the format of 3300 memory in pages. A full 16 bit address can reference byte addresses from 0 to  $65,535_{10}$ . The 16 bit address can also be considered to consist of a high order 8 bits which express the page address and a low order 8 bits which express the byte location within that page:

| <b></b> | 16 Bit Memory Address |                       |  |  |  |  |  |  |  |  |  |

|---------|-----------------------|-----------------------|--|--|--|--|--|--|--|--|--|

|         | Page Address          | Location with Page    |  |  |  |  |  |  |  |  |  |

| LZ      | 0 [7                  | 0                     |  |  |  |  |  |  |  |  |  |

|         | 256 Pages:            | 256 byte addresses    |  |  |  |  |  |  |  |  |  |

|         | Addresses from        | within each page:     |  |  |  |  |  |  |  |  |  |

|         | 0 to 255 Decimal      | From 0 to 255 Decimal |  |  |  |  |  |  |  |  |  |

|         | or                    | or                    |  |  |  |  |  |  |  |  |  |

|         | 00 to FF Hexidecimal  | 00 to FF Hexidecimal  |  |  |  |  |  |  |  |  |  |

#### A. Current Page Addressing

A Wang 3300 instruction is made up of two bytes, (16 bits). For memory reference instructions, the first byte contains the instruction operation code and information defining the mode of addressing. The second byte generally contains an operand address or jump address. Therefore, the second 8-bit byte of the instruction can normally refer to the 256 locations within the current page in which the instruction is located. This is called current page addressing.

#### FIG. 2. WANG 3300 MEMORY PAGE FORMAT

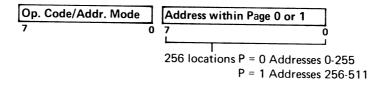

#### B. Absolute Page Addressing

Absolute page addressing is similar in format to current page addressing. However, the 8-bit address portion of the instruction indicates a location within page 0 or page 1 which is being referenced instead of the current page where the instruction is located. Page 0 is referenced if the P status register bit is currently set to 0, page 1 is referenced if P is set to 1. Therefore, an instruction located anywhere in memory can directly reference these two pages.

# 16 Bit instruction with Absolute Page Reference

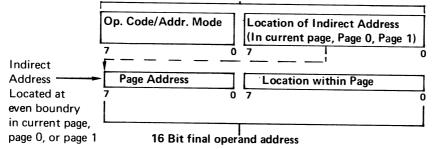

# C. Indirect Addressing

In the indirect addressing mode, the 8 bit address portion of the instruction specifies the location (within the current page, or page 0 or page 1) where the full 16 bit address of the operand is located. Thus, any location in memory can be referenced indirectly. The indirect address must be located on an even address boundary (at an even address). It acts as a pointer to a second location where the final operand is located.

16 Bit Instruction with Indirect Address Reference

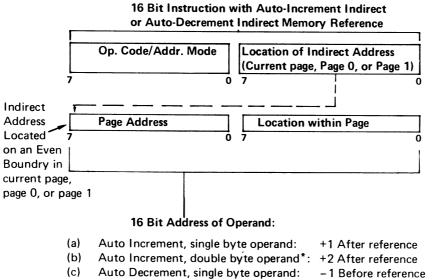

#### D. Auto-Index Indirect Address Reference

A group of Wang 3300 memory reference instructions have in addition to normal indirect addressing capability, a mode whereby the indirect address is incremented or decremented after or before it is referenced indirectly. This permits lists or tables to be processed efficiently without the bookkeeping generally necessary with indexing operations. The following two modes of auto-index indirect addressing are available:

#### (1) Auto Incrementing Indirect Mode

An operand is referenced via an indirect address. After the indirect address is referenced to obtain the operand, it is incremented. For single byte memory reference command the final value of the indirect address is one greater than the original value. For double byte memory reference commands, the final value is two greater. The indirect address must be located on an even boundry. In addition, for double byte memory reference commands the original value of the indirect address must also be even.

#### (2) Auto Decrementing Indirect Mode

An operand is referenced via an indirect address. Before the indirect address is referenced to obtain the operand, it is decremented. For single byte memory reference commands, the final value of the indirect address is one less than the original value. For double byte memory reference commands, the final value of the indirect address is two less than the original value. The indirect address must be located on an even boundry. In addition, for double byte memory reference commands, the original value of the indirect address must also be even.

#### (d) Auto Decrement, double byte operand\*: -2 Before reference

\*Original value of indirect address must be even.

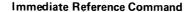

#### E. Immediate Reference

The Wang 3300 has a group of immediate reference commands. In this mode the second byte of the instruction is treated as the operand and is loaded or used in arithmetic, logical, and comparison commands.

#### **V. INSTRUCTION FORMATS**

All Wang 3300 instructions occupy two bytes of memory. They can be classified into the following six formats:

#### A. Format 1 - Memory Reference Instructions (Without Auto-Index)

This format class includes all memory reference instructions which cannot be used with autoindexing. For this format the left six bits of the operation code byte contain the op code, the right two bits specify the addressing mode. The second byte of the instruction contains the 8 bit address of the operand or indirect address within the current or an absolute page, (page 0 or page 1). For absolute page reference, page 0 is selected if the P status register bit is 0, page 1 is selected if the P status register bit is set to 1.

| Γ | 0 | Op. Code XX |   |   |   | X | M (address) |   |   |   |   |   |   |   | FORMAT 1 |  |

|---|---|-------------|---|---|---|---|-------------|---|---|---|---|---|---|---|----------|--|

| 7 | 6 | 5           | 4 | 3 | 2 | 1 | 0           | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0        |  |

#### Memory Reference Mode

XX = 00 absolute page direct

XX = 01 absolute page indirect

XX = 10 current page direct

XX = 11 current page indirect

M = Address of the operand or indirect address operand within the current page or an absolute page

#### B. Format 2 - Memory Reference Instructions (With Auto-Index)

This format class includes all memory reference instructions that can be used in auto-index addressing mode. In this format, the left 5 bits of the OP Code byte contain the Op Code, the right 3 bits specify the addressing mode. The second byte of the instruction specifies the 8 bit address of either the operand or indirect address within the current or an absolute page.

|                       | Op. Code XXX           | M (address)               |  |  |  |  |  |  |

|-----------------------|------------------------|---------------------------|--|--|--|--|--|--|

| 7 6                   | 6 5 4 3 2 1 0          | 7 6 5 4 3 2 1 0           |  |  |  |  |  |  |

| Memory Reference Mode |                        |                           |  |  |  |  |  |  |

| XXX = 000             | absolute page, direct  | M = Address of Operand or |  |  |  |  |  |  |

| XXX = 001             | absolute page, indired | ct Indirect Address with  |  |  |  |  |  |  |

| XXX = 010             | current page, direct   | the Current or an         |  |  |  |  |  |  |

| XXX = 011             | current page, indirect | t Absolute Page           |  |  |  |  |  |  |

| XXX = 100             | absolute page, indire  | ect with                  |  |  |  |  |  |  |

|                       | auto-increment         |                           |  |  |  |  |  |  |

| XXX = 101             | absolute page, indire  | ct with auto-decrement    |  |  |  |  |  |  |

| XXX = 110             | current page, indirect | t with auto-increment     |  |  |  |  |  |  |

| XXX = 111             | current page, indirec  | t with auto-decrement     |  |  |  |  |  |  |

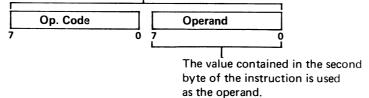

#### C. Format 3 - Immediate Reference Instructions

In this format class, the second byte of the instruction is used as the operand. It is either loaded into the Z or A registers or used directly in arithmetic, logical, or comparison operations. The entire 8 bits of the operation byte is used for the OP Code.

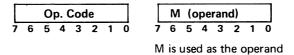

# D. Format 4 - Register Setting and Skip Instructions

In this class, the second byte of the instruction is generally used as a mask to specify which bits of a particular register will be tested by a skip instruction or set.

|   | Op. Code |   |   |   |   |   |   |   |

|---|----------|---|---|---|---|---|---|---|

| 7 | ,        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

M = Mask to specify what bits in a register are to be set or tested.

# E. Format 5 - Shift/Rotate Instructions (A-Register)

This format class includes A-register shift and rotate instructions. The rightmost two bits of the second instruction byte specify the shift count. The remaining bits in this byte are unused.

|   | Op. Code |   |   |   |   | Γ | Unused |   |     | NN  |    |       |     |      |     |   |      |

|---|----------|---|---|---|---|---|--------|---|-----|-----|----|-------|-----|------|-----|---|------|

| 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0      | 7 | 6   | 5   | 4  | 3     | 2   | 1    | 0   |   |      |

|   |          |   |   |   |   |   |        | N | N : | = ( | Sh | ift ( | Cou | int  |     |   |      |

|   |          |   |   |   |   |   |        |   | N   | N   | =  | 00    | Sł  | nift | t   | 1 | bit  |

|   |          |   |   |   |   |   |        |   | Ν   | N   | =  | 01    | Sł  | hift | t : | 2 | bits |

|   |          |   |   |   |   |   |        |   | N   | N   | =  | 02    | Sł  | hift | t : | 3 | bits |

|   |          |   |   |   |   |   |        |   | N   | N   | =  | 03    | Sł  | nift | t 4 | 4 | bits |

# F. Format 6 - Mini Instructions (Current Page Jump)

In this format class, the instruction generally performs register manipulations or input/output, and does not explicitly require the second instruction byte. It is used in all cases to perform a jump to any other location within the current page of the instruction.

|   | Op. Code |   |   |   |   |   | Γ | M (Jump Address) |   |   |   |   |   |   |   |

|---|----------|---|---|---|---|---|---|------------------|---|---|---|---|---|---|---|

| 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0 | 7                | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

M specifies the current page address of the next instruction to be executed.

#### VI. WANG 3300 INSTRUCTION REPERTOIRE

The Wang 3300 has 68 instructions. Each instruction occupies two bytes of memory. The instruction can be classified into the following functional groups:

- Memory Reference Group (Without Auto-Index)

- Memory Reference Group (With Auto-Index)

- Immediate Reference Group

- Shift and Rotate Group

- Conditional Jump Group

- Conditional Skip Group

- Register Transfer And Manipulation Group

- Input/Output And Interrupt Group

The instructions are described in detail in this section by functional group. Along with the op code and instruction description, the instruction timing and status bits effected are listed. The timing is given in memory cycles. Each memory cycle takes 1.6  $\mu$  sec. In instances where the instruction can use indirect address reference, both the direct and indirect timing are given. All indirect address memory references require two additional memory cycles.

For example, if an instruction lists the following timing:

3, 5 memory cycles

It will take: 3 memory cycles or 3 (1.6) =  $4.8 \mu$  sec. to execute with direct memory reference and 5 memory cycles or 5 (1.6) =  $8.0 \mu$  sec. to execute with indirect memory reference

The status bits effected by the execution of the instruction are listed for each instruction. For example:

Status – C, Z, V

Means that the instruction when executed will set the C (carry), Z (Last Result Zero), and V (Last Result Valid Decimal) Status Register Bits. The status register bits which can be set by instruction execution (other than status register instructions) are:

|                       | C — Carry<br>Z — Last Result Zero<br>V — Last Result Valid                                                                               | Decimal <b>(Se</b> t only i                 | n Decimal Arithmetic Mode)               |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------------|

| A. Memory Reference G | roup (Without Auto-Index)                                                                                                                | Bits 0 and 1<br>of Instruction<br>Code Byte | Assembler<br>Symbolic<br>Representation  |

| Addressing Modes:     | <ul> <li>Absolute Page, Direct</li> <li>Absolute Page, Indirect</li> <li>Current Page, Direct</li> <li>Current Page, Indirect</li> </ul> | XX = 00<br>XX = 01<br>XX = 10<br>XX = 11    | BA TAGO<br>BA* TAGO<br>BA TAG<br>BA* TAG |

| Notes: • The indi     | rect address must be located on a                                                                                                        | n even address bound                        | lary.                                    |

Memory reference instructions which reference a current page address and require more than two memory cycles for execution will not function properly when located in the last location of a page, (XXFE).

| BA | Boolean And | 010010XX                                     | м              | 3, 5 Memory Cycles                     | Status – Z, V         |

|----|-------------|----------------------------------------------|----------------|----------------------------------------|-----------------------|

|    |             | 7 0 7<br>The contents of<br>of the A-Registe |                | e memory address are and is left in A. | led with the contents |

| BO | Boolean Or  | 010110XX                                     | м              | 3, 5 Memory Cycles                     | Status – Z, V         |

|    |             | 7 0 7                                        | 0              |                                        |                       |

|    |             | The contents of                              | f the effectiv | e memory address are or                | ed with the contents  |

|          |                           |                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                                                                                      |                                                                                                                                        |                                                                                                                                                                                    |

|----------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BX       | Boolean                   | 010100XX                                                                                                                                                                                                                                                                                                         | м                                                                                                                                                                                                      | 3, 5 Memory Cycles                                                                                                                     | Status – Z, V                                                                                                                                                                      |

|          | exclusive or              | 7 0                                                                                                                                                                                                                                                                                                              | 7                                                                                                                                                                                                      | 0                                                                                                                                      |                                                                                                                                                                                    |

|          |                           | The contents the A-Registe                                                                                                                                                                                                                                                                                       | of the effe<br>er, the result                                                                                                                                                                          | ctive memory address a<br>is left in A.                                                                                                | re exclusive ored with                                                                                                                                                             |

| INC      | Increment                 | 010000XX                                                                                                                                                                                                                                                                                                         | М                                                                                                                                                                                                      | 3, 5 Memory Cycles                                                                                                                     | Status – Z, V                                                                                                                                                                      |

|          | Memory                    | 7 0                                                                                                                                                                                                                                                                                                              | 7                                                                                                                                                                                                      | 0                                                                                                                                      |                                                                                                                                                                                    |

|          |                           | The contents<br>addition is al                                                                                                                                                                                                                                                                                   | of the effe<br>ways binary.                                                                                                                                                                            | ctive memory address is                                                                                                                | incremented by one,                                                                                                                                                                |

| JEI      | Jump and                  | 010101XX                                                                                                                                                                                                                                                                                                         | M                                                                                                                                                                                                      | 2, 4 Memory Cycles                                                                                                                     | Status – None                                                                                                                                                                      |

|          | Enable                    | 7 0                                                                                                                                                                                                                                                                                                              | 7                                                                                                                                                                                                      | 0                                                                                                                                      |                                                                                                                                                                                    |

|          | Interrupt                 | made to the e                                                                                                                                                                                                                                                                                                    | effective men<br>urs or by a D                                                                                                                                                                         | t to zero, (Enable CP Int<br>nory address. (CP Interru<br>SIJ instruction). The CP                                                     | pt is disabled when an                                                                                                                                                             |

| JMP      | Jump                      | 010001XX                                                                                                                                                                                                                                                                                                         | М                                                                                                                                                                                                      | 2, 4 Memory Cycles                                                                                                                     | Status – None                                                                                                                                                                      |

|          |                           | 7 0                                                                                                                                                                                                                                                                                                              | 7                                                                                                                                                                                                      | 0                                                                                                                                      |                                                                                                                                                                                    |

|          |                           | Program Cont                                                                                                                                                                                                                                                                                                     | rol is transfer                                                                                                                                                                                        | red to the effective memo                                                                                                              | ory address.                                                                                                                                                                       |

| JST      | Jump and                  | 010011XX                                                                                                                                                                                                                                                                                                         | М                                                                                                                                                                                                      | 4, 6 Memory Cycles                                                                                                                     | Status – None                                                                                                                                                                      |

|          | Store Location            | 7 0                                                                                                                                                                                                                                                                                                              | 7                                                                                                                                                                                                      | 0                                                                                                                                      |                                                                                                                                                                                    |

| R Memor  |                           | effective mer                                                                                                                                                                                                                                                                                                    | nory addres                                                                                                                                                                                            | e next sequential instruc<br>s and effective memor<br>red to the effective mem                                                         | y address plus one.                                                                                                                                                                |

|          | N Reference Crow          | - /10/inh Auga Im.                                                                                                                                                                                                                                                                                               | <b>\</b>                                                                                                                                                                                               |                                                                                                                                        |                                                                                                                                                                                    |

| D. Memor | y Reference Group         | o (With Auto-Ind                                                                                                                                                                                                                                                                                                 | dex)                                                                                                                                                                                                   | Bits 0, 1, 2<br>of Instruction<br>Code Byte                                                                                            | Assembler<br>Symbolic<br>Representation                                                                                                                                            |

|          | sing Mode: •              | Absolute Page                                                                                                                                                                                                                                                                                                    | , Direct                                                                                                                                                                                               | Bits 0, 1, 2<br>of Instruction                                                                                                         | Assembler<br>Symbolic                                                                                                                                                              |

|          | sing Mode: ●<br>●         | Absolute Page<br>Absolute Page                                                                                                                                                                                                                                                                                   | , Direct<br>, Indirect                                                                                                                                                                                 | Bits 0, 1, 2<br>of Instruction<br>Code Byte<br>XXX = 000<br>XXX = 001                                                                  | Assembler<br>Symbolic<br>Representation                                                                                                                                            |

|          | sing Mode: ●<br>●         | Absolute Page<br>Absolute Page<br>Current Page,                                                                                                                                                                                                                                                                  | , Direct<br>, Indirect<br>Direct                                                                                                                                                                       | Bits 0, 1, 2<br>of Instruction<br>Code Byte<br>XXX = 000<br>XXX = 001<br>XXX = 010                                                     | Assembler<br>Symbolic<br>Representation<br>(ADD TAGO)<br>(ADD* TAGO)<br>(ADD TAG)                                                                                                  |

|          | sing Mode: ●<br>●         | Absolute Page<br>Absolute Page<br>Current Page,<br>Current Page,                                                                                                                                                                                                                                                 | , Direct<br>, Indirect<br>Direct<br>Indirect                                                                                                                                                           | Bits 0, 1, 2<br>of Instruction<br>Code Byte<br>XXX = 000<br>XXX = 001<br>XXX = 010<br>XXX = 011                                        | Assembler<br>Symbolic<br>Representation<br>(ADD TAGO)<br>(ADD* TAGO)<br>(ADD TAG)<br>(ADD* TAG)                                                                                    |

|          | sing Mode: ●<br>●         | Absolute Page<br>Absolute Page<br>Current Page,                                                                                                                                                                                                                                                                  | , Direct<br>, Indirect<br>Direct<br>Indirect<br>, Indirect,                                                                                                                                            | Bits 0, 1, 2<br>of Instruction<br>Code Byte<br>XXX = 000<br>XXX = 001<br>XXX = 010                                                     | Assembler<br>Symbolic<br>Representation<br>(ADD TAGO)<br>(ADD* TAGO)<br>(ADD TAG)                                                                                                  |

|          | sing Mode:<br>•<br>•<br>• | Absolute Page<br>Absolute Page<br>Current Page,<br>Current Page,<br>Absolute Page<br>Auto-Incremer<br>Absolute Page<br>Auto-Decreme                                                                                                                                                                              | , Direct<br>, Indirect<br>Direct<br>Indirect<br>, Indirect,<br>nt<br>, Indirect<br>nt                                                                                                                  | Bits 0, 1, 2<br>of Instruction<br>Code Byte<br>XXX = 000<br>XXX = 001<br>XXX = 010<br>XXX = 011<br>XXX = 100<br>XXX = 101              | Assembler<br>Symbolic<br>Representation<br>(ADD TAGO)<br>(ADD* TAGO)<br>(ADD TAG)<br>(ADD* TAG)                                                                                    |

|          | sing Mode:<br>•<br>•<br>• | Absolute Page<br>Absolute Page<br>Current Page,<br>Current Page,<br>Absolute Page<br>Auto-Incremer<br>Absolute Page<br>Auto-Decreme<br>Current Page,                                                                                                                                                             | , Direct<br>, Indirect<br>Direct<br>Indirect<br>, Indirect,<br>nt<br>, Indirect<br>nt<br>Indirect                                                                                                      | Bits 0, 1, 2<br>of Instruction<br>Code Byte<br>XXX = 000<br>XXX = 001<br>XXX = 010<br>XXX = 011<br>XXX = 100                           | Assembler<br>Symbolic<br>Representation<br>(ADD TAGO)<br>(ADD* TAGO)<br>(ADD TAG)<br>(ADD* TAG)<br>(ADD+ TAGO)                                                                     |

|          | sing Mode:<br>•<br>•<br>• | Absolute Page<br>Absolute Page,<br>Current Page,<br>Current Page,<br>Absolute Page<br>Auto-Incremer<br>Absolute Page<br>Auto-Decreme<br>Current Page,<br>Auto-Incremer                                                                                                                                           | , Direct<br>, Indirect<br>Direct<br>Indirect<br>, Indirect,<br>nt<br>, Indirect<br>nt<br>Indirect                                                                                                      | Bits 0, 1, 2<br>of Instruction<br>Code Byte<br>XXX = 000<br>XXX = 001<br>XXX = 010<br>XXX = 011<br>XXX = 100<br>XXX = 101<br>XXX = 110 | Assembler<br>Symbolic<br>Representation<br>(ADD TAGO)<br>(ADD* TAGO)<br>(ADD TAG)<br>(ADD* TAG)<br>(ADD+ TAGO)<br>(ADD- TAGO)<br>(ADD+ TAGO)                                       |

|          | sing Mode:<br>•<br>•<br>• | Absolute Page<br>Absolute Page<br>Current Page,<br>Current Page,<br>Absolute Page<br>Auto-Incremer<br>Absolute Page<br>Auto-Decreme<br>Current Page,                                                                                                                                                             | , Direct<br>, Indirect<br>Direct<br>Indirect<br>, Indirect,<br>, Indirect<br>nt<br>Indirect<br>nt<br>Indirect,                                                                                         | Bits 0, 1, 2<br>of Instruction<br>Code Byte<br>XXX = 000<br>XXX = 001<br>XXX = 010<br>XXX = 011<br>XXX = 100<br>XXX = 101              | Assembler<br>Symbolic<br>Representation<br>(ADD TAGO)<br>(ADD* TAGO)<br>(ADD TAG)<br>(ADD* TAG)<br>(ADD+ TAGO)                                                                     |

|          | sing Mode:                | Absolute Page<br>Absolute Page,<br>Current Page,<br>Current Page,<br>Absolute Page<br>Auto-Incremer<br>Absolute Page<br>Auto-Decreme<br>Current Page,<br>Auto-Incremer<br>Current Page,<br>Auto-Decreme<br>Indirect Addre<br>For double op<br>address being i<br>For Auto-Inde<br>fetch, decreme<br>For Double o | , Direct<br>, Indirect<br>Direct<br>Indirect<br>, Indirect,<br>nt<br>Indirect<br>nt<br>Indirect<br>nt<br>sses must be<br>perand comm<br>ncremented c<br>ex Indirect A<br>enting will oc<br>perand comm | Bits 0, 1, 2<br>of Instruction<br>Code Byte<br>XXX = 000<br>XXX = 001<br>XXX = 010<br>XXX = 011<br>XXX = 100<br>XXX = 101<br>XXX = 110 | Assembler<br>Symbolic<br>Representation<br>(ADD TAGO)<br>(ADD TAGO)<br>(ADD TAG)<br>(ADD TAG)<br>(ADD TAG)<br>(ADD+ TAGO)<br>(ADD- TAGO)<br>(ADD+ TAG)<br>(ADD- TAG)<br>(ADD- TAG) |

• Memory reference instructions which reference a current page address and require more than two memory cycles for execution will not function properly when located in the last location of a page, (XXFE).

| ADD | Add                              | 10000XXX         M         3, 5 Memory Cycles         Status – V, Z           7         0         7         0                                                                                                                                                                                                                                                                                                                                                                            |

|-----|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                  | The contents of the effective memory address are added to the A-Register.<br>The carry status bit is not affected. The addition will be made in binary<br>mode if the D status register bit is 0, or in decimal mode if D is 1.                                                                                                                                                                                                                                                          |

| AC  | Add with<br>Carry                | 10001XXX         M         3, 5 Memory Cycles         Status - V,Z,C           7         0         7         0                                                                                                                                                                                                                                                                                                                                                                           |

|     |                                  | The contents of the effect memory address and the C status register bit (carry) are added to the A-Register. The C status register bit will be set to the new value of the carry resulting from the addition, (0 or 1). The addition will be made in binary mode if the D status register bit is 0, or in decimal mode if D is 1.                                                                                                                                                        |

| AMC | Add to<br>Memory with<br>Carry   | 10011XXX         M         3, 5 Memory Cycles         Status – V,Z,C           7         0         7         0                                                                                                                                                                                                                                                                                                                                                                           |

|     |                                  | The contents of the A-Register and the C Status Register bit (carry) are added to contents of the effective memory address. The C Status Register bit will be set to the new value of the carry resulting from the addition, (0 or 1). The addition will be made in binary mode if the D status register bit is 0, or in decimal mode if D is 1.                                                                                                                                         |

| С   | Compare                          | 10010XXX         M         3, 5 Memory Cycles         Status - Z,V,C           7         0         7         0                                                                                                                                                                                                                                                                                                                                                                           |

|     |                                  | The 2's complement of the contents of the A-Register and the contents of effective memory address are added together in binary mode. The result is not saved but the Z (result zero) and C (carry) status register bits are set. The comparison jumps JGT, JNE, JLT, JEQ can be used subsequently.                                                                                                                                                                                       |

| DAM | Double Add<br>to Memory          | 10101XXX         M         4, 6 Memory Cycles         Status - Z,V,C           7         0         7         0         7                                                                                                                                                                                                                                                                                                                                                                 |

|     |                                  | The contents of the Z and A registers and the C status register bit (carry) are added to the two byte contents of the effective memory address and memory address + 1. The C status register bit (carry) is set to the new carry resulting from the two byte addition. The addition will be made in binary mode if the D status register bit is 0, or in decimal mode if D is 1. The Z status bit reflects both bytes of the result. The V status bit reflects only the high order byte. |

| DCM | Double<br>Compare with<br>Memory | 10100XXX         M         4, 6 Memory Cycles         Status - C,Z,V           7         0         7         0         7         0                                                                                                                                                                                                                                                                                                                                                       |

|     | ,                                | The 2's complement of the contents of the Z and A registers and the two byte contents of the effective memory address, and memory address $+ 1$ are added together. The result is not saved but the Z (result zero) and C (carry) status register bits are set. The comparison jumps, JGT, JNE, JLT, and JEQ can be used subsequently. The Z status bit reflects the result of both bytes. The V status bit reflects only the high order byte.                                           |

| DL  | Double Load                      | 10110XXX         M         4, 6 Memory Cycles         Status - Z, V           7         0         7         0                                                                                                                                                                                                                                                                                                                                                                            |

The contents of the effective memory location is loaded into the Z register, the contents of the effective memory location + 1 is loaded into the A-register. The V status bit reflects only the high order byte loaded, (final contents of Z register), while the Z status bit reflects the result of both bytes.

| <b></b>   |                          |                                                                                                                                                                                                                               |

|-----------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DU        | Double<br>Unload         | 10111XXX M 4, 6 Memory Cycles Status – None                                                                                                                                                                                   |

|           | Onioau                   |                                                                                                                                                                                                                               |

|           |                          | The contents of the Z register replaces the contents of the effective                                                                                                                                                         |

|           |                          | memory address, the contents of the A-register replaces the contents of                                                                                                                                                       |

|           |                          | the effective memory address + 1.                                                                                                                                                                                             |

| LA        | Load A                   | 11000XXX M 3,5 Memory Cycles Status – Z, V                                                                                                                                                                                    |

|           |                          |                                                                                                                                                                                                                               |

|           |                          | The contents of the effective memory address is loaded into the A-Register.                                                                                                                                                   |

| LZ        | Load Z                   | 11010XX         M         3, 5 Memory Cycles         Status - Z, V           7         0         7         0                                                                                                                  |

|           |                          | The contents of the effective memory address is loaded into the Z Register.                                                                                                                                                   |

| UA        | Unload A<br>(Store A)    | 11001XX         M         3,5 Memory Cycles         Status - None           7         0         7         0                                                                                                                   |

|           |                          | The contents of the A-Register replace the contents of the effective memory address.                                                                                                                                          |

| UAH       | Unload A<br>High Digit   | 11101XXX         M         3, 5 Memory Cycles         Status - None           7         0         7         0                                                                                                                 |

|           |                          | Bits 7 - 4 of the A register replaces bits 7 - 4 of the contents of the effective memory address.                                                                                                                             |

| UZ        | Unload Z<br>(Store Z)    | 11011XXX         M         3, 5 Memory Cycles         Status - None           7         0         7         0                                                                                                                 |

|           |                          | The contents of the Z register replace the contents of the effective memory address.                                                                                                                                          |

| XMA       | Exchange<br>Memory and A | 11100XXX         M         3,5 Memory Cycles         Status - V, Z           7         0         7         0                                                                                                                  |

|           |                          | The contents of the effective memory address is exchanged with the contents of the A-register. (V, Z status bits reflect final contents of the A-register.)                                                                   |

| C. Immedi | ate Reference Gr         | oup                                                                                                                                                                                                                           |

| All inst  | ructions use the s       | econd byte of the instruction, M, as an operand.                                                                                                                                                                              |

| AI        | Add<br>Immediate         | 00011000         M         2 Memory Cycles         Status - V, Z           7         0         7         0         7                                                                                                          |

|           |                          | The second byte of the instruction, M, is added to the A register. The status register C bit (carry) is not affected. The addition is performed in binary mode if the D status bit is set to 0, or in decimal mode if D is 1. |

| BAI       | Boolean AND<br>Immediate | 00011101         M         2 Memory Cycles         Status - V,Z           7         0         7         0                                                                                                                     |

|           |                          | The second byte of the instruction, M, is anded with the contents of the                                                                                                                                                      |

|           |                          | A-register, the result is stored in A.                                                                                                                                                                                        |

| BOI       | Boolean OR<br>Immediate  | 00011111         M         2 Memory Cycles         Status - V, Z           7         0         7         0                                                                                                                    |

|           |                          | The second byte of the instruction Main and initial                                                                                                                                                                           |

|           |                          | The second byte of the instruction, M, is ored with the contents of the A-register, the result is stored in A.                                                                                                                |

| BXI | Boolean<br>Exclusive or<br>Immediate | 00011110M2 Memory CyclesStatus - V, Z7070The second byte of the instruction, M, is Exclusive Ored with the contents of the A-register, the result is stored in A.                                                                                                                                                                                                                          |

|-----|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СІ  | Compare<br>Immediate                 | 00011001       M       2 Memory Cycles       Status - C, V, Z         7       0       7       0         The 2's complement of the contents of A and the contents of the second byte of the instruction, M, are added together. No result is saved but the Z (result zero) and C (carry) status register bits are set. The comparison jumps JGT, JNE, JLT and JEQ can be used subsequently. |

| DLI | Double Load<br>Immediate             | 00011100M2 Memory CyclesStatus - C,V,Z7070The second byte of the instruction, M, replaces the contents of the A-register. The high order bit of M, $(M_7)$ , is propagated thru the Z-register. The C status bit, (carry) is set to 0.                                                                                                                                                     |

| LAI | Load A-<br>Register<br>Immediate     | 00011010M2 Memory CyclesStatus - V, Z7070The second byte of the instruction, M, replaces the contents of the A-register.                                                                                                                                                                                                                                                                   |

| LZI | Load Z<br>Register<br>Immediate      | 00011011     M     2 Memory Cycles     Status - V, Z       7     0     7     0       The second byte of the instruction, M, replaces the contents of the Z-register.                                                                                                                                                                                                                       |

# D. Shift and Rotate Group

For all instructions in this group except SDJ, SBJ, and SBCJ the low order two bits of the address instruction byte ( $M_0$  and  $M_1$ ), specify the shift count which can be 1 to 4 bits. The shift count for SDJ, SBJ, SBCJ is explicitly 1 bit or 1 digit (4 bits).

For all single register shift and rotate instructions the shift count, NN, is interpreted as follows:

| NN | = | 00 | Shift 1 bit  |

|----|---|----|--------------|

| NN | = | 01 | Shift 2 bits |

| NN | = | 10 | Shift 3 bits |

| ΝN | = | 11 | Shift 4 bits |

| RT | Rotate A | 00100010 | 000000NN | 2 Memory Cycles | Status – None |

|----|----------|----------|----------|-----------------|---------------|

|    | Left     | 7 0      | 7        | 0               |               |

The contents of the A-register is circularly rotated left NN bits, (1-4). Bits shifted out of  $A_7$  replace  $A_0$ .